www.ijprems.com

editor@ijprems.com

INTERNATIONAL JOURNAL OF PROGRESSIVE<br/>RESEARCH IN ENGINEERING MANAGEMENT<br/>AND SCIENCE (IJPREMS)e-ISSN :<br/>2583-1062AND SCIENCE (IJPREMS)<br/>(Int Peer Reviewed Journal)Impact<br/>Factor :<br/>7.001

# **'INTELLIGENT FAULT CLASSIFICATION AND INVESTIGATION OF TRANSMISSION FAULT DETECTION**

Prashant Soni<sup>1</sup>, Dhanendra Singh<sup>2</sup>, Adarsh Kumar Gupta<sup>3</sup>, Abhishek<sup>4</sup>, Raginee Patle<sup>5</sup>, Sridhar Burla<sup>6</sup>

1,2,3,4,5UG Student, EEE, Oriental Institute of Science and Technology, Bhopal, M.P., India.

<sup>6</sup>Assistant Professor, EEE, Oriental Institute of Science and Technology, Bhopal, M.P., India.

## ABSTRACT

An important emerging area for VLSI systems is power grids, micro grids, and their transmission lines. Transmission line protection is an important issue in power system engineering because more than 80% of system faults occur in transmission lines. Most of those systems are three phase systems. This paper presents a method for monitoring those three phases on a single output line from a micro-controller, which we have named as T-line. This innovation is important since a power network has multiple transmission lines emerging from a generator station. The paper also presents the concept for detecting the type of fault to estimate the distance and severity of the fault from that  $\Gamma$ -line. As in second part of the paper, another micro-controller is used to compute the running DFT/FFT of a signal in real time. A VLSI Architecture for some parts of the algorithm is also presented. The micro-controller is TI TMS320F28335 applied to detect the fault to get the required results.

Keywords: Microcontroller, micro grid, Transmission Line Fault

### **1. INTRODUCTION**

Transmission lines (TLs) play a crucial role in power systems by linking generation stations to end-users, ensuring a continuous power supply. Additionally, they facilitate bidirectional power flow between interconnected systems, enabling efficient energy transfer. High-voltage TLs are particularly effective in transmitting large amounts of electrical power between different regions in a cost-efficient manner. Given that TLs are prone to faults, a reliable protection mechanism is necessary to safeguard the electrical network. TL faults are typically categorized into three main types: shunt unsymmetrical, shunt symmetrical, and series faults. Unsymmetrical shunt faults include single line-to-ground (SLG), double line (DL), and double line-to-ground (DLG) faults, while symmetrical shunt faults primarily consist of three-phase (3L or 3LG) faults. These transient faults can result in excessive voltage or current levels, potentially damaging insulation materials and conductors depending on their intensity. However, the data generated by these faults can be valuable for analysing disturbances in TLs. To maintain system stability, reliability, and power quality, it is essential to detect, classify, and locate faults swiftly and accurately. Protective relays play a key role in this process by analysing three-phase currents, voltages, or both to identify faults, determine the affected phases, classify fault types, and pinpoint fault locations. Once a fault is detected, the relays send a tripping signal to circuit breakers (CBs) to isolate the faulty TL from the rest of the power network. Traditional distance relays serve as the primary protection method for TLs, estimating the impedance between the relay and the fault location to determine the fault's distance. Key protection parameters for TLs include the relay's speed, reliability, and accuracy in fault detection and classification. With advancements in signal processing and modern technologies, fault diagnosis in TL protection has significantly evolved. Various methodologies have been explored in research studies to enhance fault detection, classification, location identification, phase selection, and fault direction determination.

## 2. METHODOLOGY

Transmission line (TL) fault detection is a crucial aspect of power system protection, ensuring system reliability and stability. Various techniques have been developed over time to quickly and accurately detect, classify, and locate faults in TLs. These techniques can be broadly classified into traditional and modern approaches.

1. Conventional Fault Detection Techniques

a) Impedance-Based (Distance Relay) Method

Utilizes the measurement of voltage and current to estimate the impedance between the relay and the fault location. If the impedance value falls within a predefined range, the relay detects a fault and sends a trip signal to isolate the faulted section. Commonly used in high-voltage transmission systems.

b) Overcurrent Protection

Detects excessive current flow caused by short circuits. Uses a predetermined threshold; if the fault current exceeds this limit, the relay triggers a circuit breaker to disconnect the affected section. Works best in radial distribution systems but may face selectivity issues in interconnected networks.

|                    | INTERNATIONAL JOURNAL OF PROGRESSIVE          | e-ISSN :  |

|--------------------|-----------------------------------------------|-----------|

| IJPREMS            | <b>RESEARCH IN ENGINEERING MANAGEMENT</b>     | 2583-1062 |

| an ma              | AND SCIENCE (IJPREMS)                         | Impact    |

| www.ijprems.com    | (Int Peer Reviewed Journal)                   | Factor :  |

| editor@ijprems.com | Vol. 05, Issue 04, April 2025, pp : 1038-1041 | 7.001     |

#### c) Differential Protection

Compares incoming and outgoing currents in a TL section. If the difference exceeds a threshold, the system identifies a fault and isolates the faulty section. Offers high accuracy but requires extensive communication infrastructure.

d) Traveling Wave-Based Method

Detects and analyses high-frequency transient signals generated by faults. Measures the time difference of traveling waves at different points to locate the fault. Provides fast fault detection but requires specialized sensors and signal-processing units.

2. Modern Fault Detection Techniques

a) Wavelet Transform-Based Method

Decomposes fault signals into different frequency components using wavelet transforms. Helps detect and classify faults with high accuracy, even in noisy environments.

b) Artificial Intelligence (AI) and Machine Learning (ML)

Uses data-driven models to identify and classify faults based on historical data. Neural networks, support vector machines (SVMs), and deep learning models improve fault classification and location accuracy. Adapts to changing system conditions and reduces false positives.

c) Phasor Measurement Unit (PMU)-Based Detection

Uses synchronized phasor measurements to monitor real-time system conditions. Helps in detecting faults quickly by analysing phase angles and voltage deviations.

d) Hybrid Techniques

Combines traditional and modern approaches to enhance detection speed and accuracy. For example, integrating wavelet transforms with AI-based models improves fault classification and location estimation.

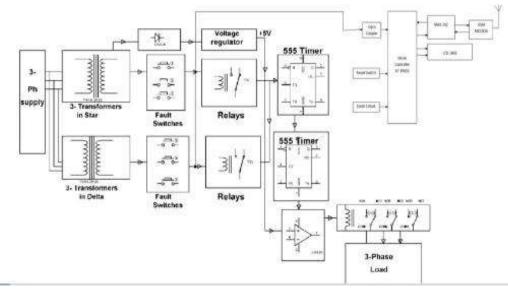

#### Working with Block Diagram

#### Fig. 1. Circuit Diagram Working

The model uses 4 numbers step-down transformers for handling the entire circuit under low voltage conditions of 12v only to test the 3 phase fault analysis. The primaries of transformers are connected to a 3 phase supply in star configuration, while the secondary of the same is also connected in star configuration. The other set of transformers with its primary connected in star to 3 phase have their secondary connected in Delta configuration. The outputs of all the transformers are rectified and filtered individually and are given to 6 relay coils. 6 push buttons, every button connected across the relay coil is meant to create a fault condition either at star i.e. LL Fault or 3L Fault. The NC contacts of all the relays are made parallel while all the common points are grounded. The parallel connected points of NC are given to pin2 through a resistor R5 to a 555 timer i.e. wired in mono-stable mode. The output of the same timer is connected to the reset pin 4 of another 555 timer from pin3 is given to an Op-amp LM358 through wire 11 and d12 to the non-inverting input pin3, while a potential divider RV2 keeps the inverting input at fixed voltage. The voltage at pin2 coming from the RV2 (potential divider) is held such that it is higher than the voltage at pin3 of the Op-amp used as a comparator.

#### Fig. 2. Flow Chart

The AT89C51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K bytes of flash programmable and erasable read only memory (PEROM). The device is manufactured using ATMEL's high density non-volatile memory technology and is compatible with the industry-standard MCS-51 instruction set and pin out. The on-chip Flash allows the program memory to be reprogrammed in-system or by a conventional non-volatile memory programmer. By combining a versatile 8-bit CPU with Flash on a monolithic chip, the ATMEL AT89C51 is a powerful microcomputer which provides a highly-flexible and cost-effective solution to many embedded control applications.

As a result, pin1develops zero logic that fails to operate the relay through the driver transistor Q1. This relay Q1 is 3CO relay i.e. it disconnects the load to indicate fault condition.

#### **Investigation Analysis**

The proposed approach has been designed for use across diverse locations, phases, resistances, and fault durations on both sides of the line. Ultimately, by employing the estimated phasors, the impedance and, consequently, the distance from the fault location to the relay may be accurately determined, eliminating the necessity to alter the configuration and formulation of the distance relay. The approach has undergone testing and evaluation for various short circuit scenarios on both sides of the line under diverse conditions.

However, the benefits are numerous as this will lead to the desirable features as: Timely intervention against faults, Real-time data capture and prediction, Adaptive programming, Device compatibility and suitability in embedded processors, Transient Stability. It also has the impact on Post-Fault Recovery and Synchronization.

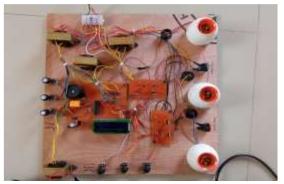

Fig.3. Working model

| IJPREMS            | INTERNATIONAL JOURNAL OF PROGRESSIVE<br>RESEARCH IN ENGINEERING MANAGEMENT | e-ISSN :<br>2583-1062 |

|--------------------|----------------------------------------------------------------------------|-----------------------|

| an ma              | AND SCIENCE (IJPREMS)                                                      | Impact                |

| www.ijprems.com    | (Int Peer Reviewed Journal)                                                | Factor :              |

| editor@ijprems.com | Vol. 05, Issue 04, April 2025, pp : 1038-1041                              | 7.001                 |

## 3. RESULT DISCUSSION

Various faults have been created to develop an automatic tripping mechanism for the three phase supply system while temporary fault and permanent faults occur. Here timer 555 has been used with relay for the analysis. Short duration fault returns the supply to the load immediately called as temporary trip while long duration shall result in permanent trip. Also we adjust the time duration for permanent fault by adjusting capacitors charging periods. Whenever any type of fault: LG temporary/permanent or LL temporary / permanent & under voltage and over voltage occurs regarding faults is displayed on LCD.

Fig. 4. Fault Detection and trip result

## 4. CONCLUSION

This three phase fault analysis system is built using single phase transformers. The input to the transformers is 220 volt and output is 12 volt. For introducing faults on the low voltage side, set of switches are used that create LL, LG, and 3L faults. The supply returns to the load in the case of a short duration fault and is referred as a temporary trip while long duration disconnection of supply and load shall result in a permanent trip.

Acknowledgement: The authors are highly grateful to Oriental Institute of Science and Technology, faculties of electrical and electronics engineering department, Bhopal and the project cell for providing the state-of-the-art platform required for research facilities.

## 5. REFERENCES

- N. Baeckeland, D. Venkatramanan, S. Dhople, and M. Kleemann, "On the distance protection of power grids dominated by grid-forming inverters," in 2022 IEEE PES Innovative Smart Grid Technologies Conference Europe (ISGT-Europe), 2022, pp. 1–6.

- [2] Mukherjee, A., Kundu, P.K. & Das, A. Transmission Line Faults in Power System and the Different Algorithms for Identification, Classification and Localization: A Brief Review of Methods. J. Inst. Eng. India Ser. B 102, 855–877 (2021). https://doi.org/10.1007/s40031-020-00530-0.

- [3] Liang, Y. et al. A robust and accurate discrete fourier transform-based phasor estimation method for frequency domain fault location of power transmission lines. IET Gener. Transmi. Distrib. 16 (10), 1990–2002 (2022).

- [4] Chatterjee, B. & Debnath, S. Sequence component based approach for fault discrimination and fault location estimation in UPFC compensated transmission line. Electr. Power Syst. Res. 180, 106155 (2020)

- [5] Banaiemoqadam, A., Hashemi, S.M., Hooshyar, A.: Loss-of-voltage detection for relays protecting systems with inverter-based resources. IEEE Trans. Power Delivery 37(1), 674–689 (2022)

- [6] Srivastava, A., Mohanty, R., Ghazvini, M.A.F., Tuan, L.A., Steen, D., Carlson, O.: A review on challenges and solutions in microgrid protection, IEEE Madrid PowerTech, pp. 1–6 (2021)

- [7] X. Li, Y. Lu, W. Jiang, and J. Qin, "Compensated phase selection method based on virtual magnitude rezoning for transmission lines emanating from wind farms," Electr. Power Syst. Res., vol. 206, May 2022, Art. no. 107804.

- [8] V. K. Gaur, S. Chakrabarti, and A. Sharma, "Improving faulty phase selection in PV integrated system with compensation angle approach," Electr. Power Syst. Res., vol. 226, Jan. 2024, Art. no. 109913.

- [9] H. Zhang, W. Xiang, Q. Hong, and J. Wen, "Active phase control to enhance distance relay in converter-interfaced renewable energy systems," Int. J. Electr. Power Energy Syst., vol. 143, Dec. 2022, Art. no. 108433.

- [10] A. A. Aboelnaga and M. A. Azzouz, "Dual current control of renewable energy sources for recent grid code compliance and reliability enhancement," IEEE Trans. Sustain. Energy, vol. 15, no. 2, pp. 1380–1395, Apr. 2024.

- [11] M. A. Azzouz, A. Hooshyar, and E. F. El-Saadany, "Resilience enhancement of microgrids with inverterinterfaced DGs by enabling faulty phase selection," IEEE Trans. Smart Grid, vol. 9, no. 6, pp. 6578–6589, Nov. 2018.

- [12] A. A. Aboelnaga, M. A. Azzouz, A. S. A. Awad, and H. F. Sindi, "Dual current control of inverter-based resources for enhanced resilience and complying grid codes," in Proc. IEEE PES Conf. Innov. Smart Grid Technol.-Middle East (ISGT Middle East), Mar. 2023, pp. 1–5.